Cadence & Micron DDR5 Update: 16 Gb Chips on Track for 2019

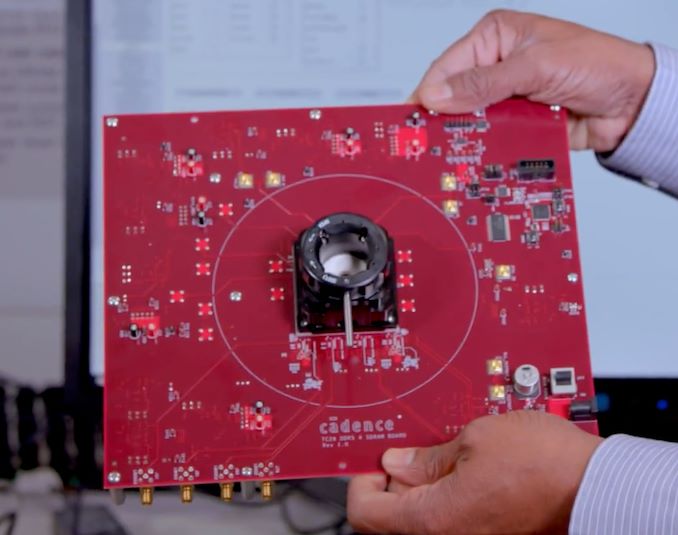

Earlier this year Cadence and Micron performed the industry’s first public demonstration of next-generation DDR5 memory. At a TSMC event earlier this month the two companies provided some updates concerning development of the new memory technology. As it appears, the spec has not been finalized at JEDEC yet, but Micron still expects to start production of DDR5 memory chips in late 2019.

As noted back in May, the primary feature of DDR5 SDRAM is capacity of chips, not just a higher performance and a lower power consumption. DDR5 is expected to bring in I/O speeds of 4266 to 6400 MT/s, with a supply voltage drop to 1.1 V and an allowable fluctuation range of 3% (i.e., at ±0.033V). It is also expected to use two independent 32/40-bit channels per module (without/or with ECC). Furthermore, DDR5 will have an improved command bus efficiency (because the channels will have their own 7-bit Address (Add)/Command (Cmd) buses), better refresh schemes, and an increased bank group for additional performance. In fact, Cadence goes as far as saying that improved functionality of DDR5 will enable a 36% higher real-world bandwidth when compared to DDR4 even at 3200 MT/s (this claim will have to be put to a test) and once 4800 MT/s speed kicks in, the actual bandwidth will be 87% higher when compared to DDR4-3200. In the meantime, one of the most important features of DDR5 will be monolithic chip density beyond 16 Gb.

Leading DRAM makers already have monolithic DDR4 chips featuring a 16 Gb capacity, but those devices cannot offer extreme clocks or I/O speeds because of laws of physics. Therefore, companies like Micron have a lot of work to do in a bid to bring together high DRAM densities and performance in the DDR5 era. In particular, Micron is concerned about variable retention time, and other atomic level occurrences, once production technologies used for DRAM reach 10 – 12 nm. Meanwhile, the DDR5 Add/Cmd bus already features on-die termination to make signals cleaner and to improve stability at high data rates. Furthermore, high-end DDR5 DIMMs will have their own voltage regulators and PMICs. Long story short, while the DDR5 standard is tailored to wed performance and densities, there is still a lot of magic to be done by DRAM manufacturers.

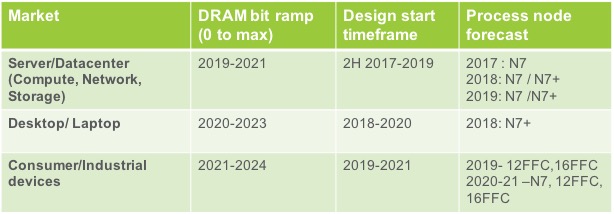

Micron expects to start production of 16 Gb DDR5 chips using its “sub-18nm” fabrication process late in 2019, though this does not necessarily mean that actual applications featuring this memory will be available by the end of next year. Cadence already has DDR5 IP (controller + PHY) implemented using TSMC’s N7 (7 nm DUV) and N7+ (7 nm DUV+EUV) process technologies, so chip developers have what they need to design SoCs compatible with the new type of memory. Cadence is working on DDR5 IP for more advanced process technologies.

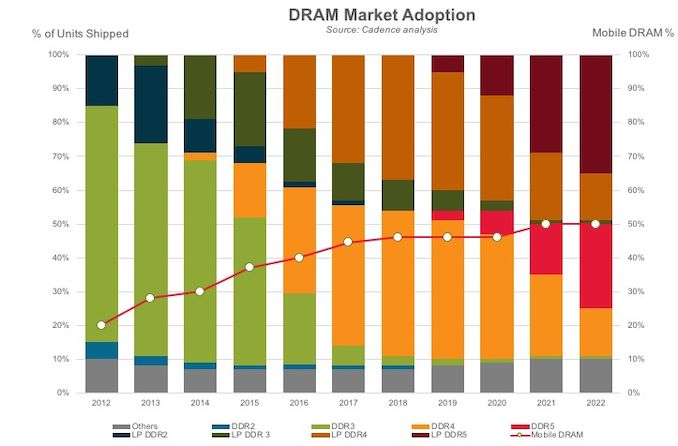

Given the key advantages of DDR5, it is not surprising that Cadence forecasts servers to be the first applications to use the new type of DRAM. What is particularly interesting is that Cadence believes that client SoCs made using N7+ process will support DDR5, which essentially means chips due to hit the market in 2020. Given rather quick ramp of DDR5 production predicted by Cadence, it looks like the new DRAM will be supported by a wide range of chips.

Related Reading:

Cadence and Micron Demo DDR5-4400 IMC and Memory, Due in 2019 JEDEC: DDR5 to Double Bandwidth Over DDR4, NVDIMM-P Specification Due Next Year Micron, Rambus, & Others Team Up To Spur GDDR6 Adoption in Non-GPU Products Samsung Updates on GDDR6 Portfolio: 8 Gb and 16 Gb at Multiple Speeds Samsung Starts Mass Production of 16Gb GDDR6 Memory ICs with 18 Gbps I/O Speed GDDR5X Standard Finalized by JEDEC: New Graphics Memory up to 14 Gbps JEDEC Publishes HBM2 Specification as Samsung Begins Mass Production of ChipsSource: Cadence

Comments

Post a Comment